研究者総覧「情報知」

情報システム学専攻

- 氏 名

- 嶋田 創(しまだ はじめ)

- 講座等

- 情報ネットワークシステム論講座

- 職 名

- 准教授

- 学 位

- 博士(工学)

- 研究分野

- グリーンコンピューティング / 情報ネットワーク / 計算機アーキテクチャ

研究内容

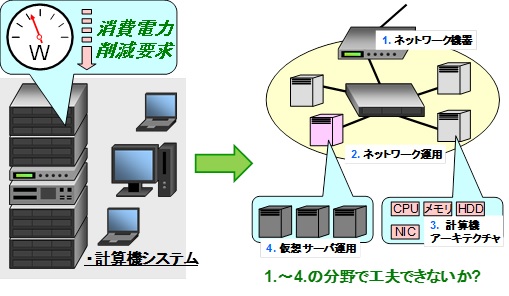

情報基盤システムの消費電力削減によるグリーンコンピューティングの実現

近年では家電等もインターネットを介して情報を受け取ることが当たり前となり、日本の全消費電力に対する、インターネットを構成するサーバやネットワーク・ルータの消費電力の割合は、年々増加する傾向にあります。具体的な数値については統計の取り方によって幅が出てきてしまいますが、「平均すると企業の消費電力の40%は情報機器関連」というデータがあり、また、「情報機器関連の消費電力の50%は空調、10%は電力変換、25%はサーバ等の計算機、10%はネットワーク機器」というデータもあります。

この情報機器が消費する電力は今後も増加すると考えられておりますが、地球規模で従来型エネルギー資源の獲得競争が激しくなっている点や二酸化炭素排出量を増加されるという点から、従来型の発電所による発電量増加は好ましくありません。とはいえ、現在発電量の増加が期待されている自然エネルギーは発電量が安定せず、安定性を要求されるサーバなどのインフラストラクチャには向きません。

この問題を緩和するために、コンピュータの消費電力を削減したり、ジョブ投入を工夫などによる消費電力の細かな調整によって発電量の安定しない自然エネルギーのもとでの安定動作を実現することにより、環境への負荷を下げる、グリーン・コンピューティング(グリーンIT)の実現が強く求められております。私は特に消費電力削減側の研究に力を入れています。消費電力の削減は一般的に、計算機性能やシステムの信頼性とトレードオフになることが多いため、「性能や信頼性を大きく落とさずに消費電力削減してよし」という形に持って行く必要があります。そこで、多少のオーバヘッドを被っても、動的に構成を変更可能な形として、部分負荷に細かく追従して消費電力を削減するアプローチをもとに研究を推進しています。

具体的な研究対象としては、以下の部分を推進しています。

1. ネットワーク機器の通信時電力制御の改善

現在ではUTPケーブルを使うイーサネットで10Gbps、無線イーサネットで1.3Gbpsの通信帯域が実現されています。高速な規格での通信は、1ビットの転送あたりの消費電力は少なくなりますが、電子回路の規模が大きくなることによって単位時間あたりの消費電力は増えます。そのため、規格においてもEnergy Efficient Ethernetなどが提唱され、無通信時のスリープによる消費電力が低減されています。私の研究では、これをさらに積極的に実施するために、アプリケーション側と連携してスリープ制御を行う研究を推進しています。

2.および4. ネットワーク運用の改善、仮想サーバ運用改善

現在ではネットワーク通信は止まると社会に重大な影響を及ぼすインフラストラクチャとなっているため、冗長化によって1つの通信経路が止まっても大きな障害にならないようにネットワークが構成されています。しかしながら、この冗長化は、緊急時以外は無用の電力を消費する物であるため、削減できるものならば削減したいものです。同様の問題はサーバ運用でも発生します。そのため、私は仮想サーバ運用とも連携し、冗長用の計算/ネットワーク資源を物理的に離れた箇所で共有して、冗長化で消費される電力を削減する研究を推進しています。

3. サーバの計算機アーキテクチャの改善

冒頭に記したように、計算機の消費電力は全体の25%を占める上、その消費電力削減は空調や電力変換による消費電力にも関連するため、昔より多数の研究が行われています。私は特に、プロセッサ内部の電子回路の構成に対して消費電力削減の工夫を盛り込むことを精力的に行っており、パイプライン構成の動的な変更、ALU間のデータ移動の工夫、動的なデータ圧縮等を利用して、消費電力を削減する研究を推進しています。

経歴

- 2004年名古屋大学博士(工学).同年名古屋大学工学部電気系COE研究員.

- 2005年京都大学大学院情報学研究科特任助手.2006年同助手.2009年奈良先端科学技術大学院大学准教授。

- 2013年名古屋大学情報基盤センター准教授。現在に至る。

所属学会

- IEEE

- 情報処理学会

- 電子情報通信学会

主要論文・著書

- 小林良太郎, 松川大佑, 下村佳生, 落合裕也, 嶋田創, "データの冗長性に着目したキャッシュの回路面積削減," 電気学会論文誌, Vol. 133, No. 8, Sec. C, pp. 1597-1606, 2013年8月.

- Jun Yao, Kosuke Ogata, Hajime Shimada, Shinobu Miwa, Hiroshi Nakashima, and Shinji Tomita, "An Instruction Scheduler for Dynamic ALU Cascading Adoption," 情報処理学会論文誌, コンピューティングシステム, Vol. 2, No. 2, pp. 30-47, 2009年7月.

- 嶋田創, 安藤秀樹, 島田俊夫, "パイプラインステージ統合によるプロセッサの消費エネルギーの削減," 情報処理学会論文誌, コンピューティングシステム, Vol. 45, No. SIG 1 (ACS 4), pp. 18-30, 2004年1月.